16-ти разрядный адрес позволяет адресовать до 64K узлов на шине

предельная теоретическая длина шины 224 метра

"горячее" подключение/отключение без потери данных

автоматическое конфигурирование, аналогичное Plug&Play

произвольная топология шины - по аналогии с локальными сетями может использоваться как "звезда" так и общая шина (только в виде цепочки, в отличие от сети на коаксиальном кабеле)

никакие терминаторы не требуются

возможность обмена с гарантированной пропускной способностью, что крайне необходимо для передачи видеоизображений

Топология шины

Топология IEEE-1394 позволяет как древовидную, так и цепочечную архитектуру, а также комбинацию из того и другого. Поэтому легко строить любые варианты подключения различных устройств к шине. Стандарт предусматривает архитектурное разделение шины на 2 основных блока - кабельная часть и контроллер (контроллеры). Так как контроллеров может быть несколько, эту часть также называют объединительной (backplane - дословно задний план, кросс-плата и т. п.).

Адрес узла на "дереве" 16-ти разрядный, что позволяет адресовать до 64К узлов. К каждому узлу может быть подключено до 16-ти конечных устройств. На объединительной панели (backplane) может быть подключено до 63 узлов к одному мосту (bridge) шины. Так как под идентификатор номера шины (моста) отведено 10 разрядов, то общее количество узлов и составляет 64K.

Каждый узел обычно предусматривает подключение 3-х устройств, хотя собственно стандарт разрешает подключение до 27 устройств. Устройства могут быть подключены через стандартные кабели длиной до 4.2 метра.

Пример топологии IEEE-1394

Физические адреса (ID) устройствам назначаются при подаче питания на контроллер шины и устройства, подключенные к ней, после общего сброса шины, а также при "горячем" подключении устройства к шине. Адреса присваиваются в порядке последовательности обнаружения и/или подключения устройств. Никакая установка перемычек или переключателей на самих устройствах не требуется.

Стандарт на кабельную часть предусматривает три скорости передачи данных по шине - 98.304, 196.608 и 393.216 Mbits/s. Обычно эти значения в различных документах огругляют до 100, 200 и 400 Mbits/s, используя для краткости обозначения S100, S200 и S400.

Благодаря применению размножителей, репитеров и т. п. устройств топология IEEE-1394 может быть достаточно сложной, хотя в 90% случаев ее применения наверняка столь сложная топология не потребуется.

Совместимость

Для удобства программирования и совместимости устройств на IEEE-1394 был разработан стандарт, названный Open Host Controller Interface (OHCI). Он предъявляет определенные требования к регистрам контроллера IEEE-1394 и их отображению в памяти. Кроме этого, OHCI совместимый контроллер должен удовлетворять требованиям по управлению энергопотреблением в соответствии со спецификацией ACPI.

Microsoft в своих операционных системах Windows 98 Second Edition и Windows 2000 поддерживает только OHCI совместимые контроллеры IEEE-1394. Все остальные контроллеры (например, от Adaptec) должны сопровождаться соответствующими драйверами и совместимость таких устройств с драйверами жестких дисков операционной системы, например, не гарантируется.

Кабели и разъемы

Стандартный кабель для IEEE-1394 состоит из 2 витых пар передачи сигналов шины, двух проводов питания и все это заключено в экранированную оболочку. Провода питания рассчитаны на ток до полутора ампер и напряжение от 8 до 40 вольт. На рисунке ниже показан один из вариантов кабеля IEEE-1394.

Кабели и розетки для подключения периферийных устройств существуют в нескольких вариантах, в зависимости от требуемых параметров:

Кабель на 6/6 проводов, поддержка скорости передачи до 400 Mbits/s. Напряжение питания до 40 V при токе до 1.5 А. Длина от 0.7 м до 4.5 м.

Кабель на 6/4 проводов, поддержка скорости передачи до 100 Mbits/s. Напряжение питания до 5 V при токе до 0.5 А. Длина от 1 м до 4.5 м.

Кабель на 4 провода, поддержка скорости передачи до 100 Mbits/s. Напряжение питания до 5 V при токе до 0.5 А. Длина от 1 м до 4.5 м.

Розетка на 4 провода, поддержка скорости передачи до 400 Mbits/s. Напряжение питания до 5 V при токе до 0.5 А.

Розетка на 6 проводов, поддержка скорости передачи до 400 Mbits/s. Напряжение питания до 40 V при токе до 1.5 А.

Список литературы

правочное пособие по цифровой электронике: Пер. с англ. — М.: Энергоатомиздат, 1990. Справочник программиста и пользователя/ Под ред. , . — М.: “Кварта”, 1993.Лекция 17. Организация прямого доступа к памяти.

Введение

Одним из способов обмена данными с ВУ является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ВУ и основной памятью ЭВМ происходит без участия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а электронные схемы, внешние по отношению к процессору. Обычно схемы, управляющие обменом в режиме ПДП, размещаются или в специальном контроллере, который называется контроллером прямого доступа к памяти, или в контроллере самого ВУ.

Обмен данными в режиме ПДП позволяет использовать в ЭВМ быстродействующие внешние запоминающие устройства, такие, например, как накопители на жестких магнитных дисках, поскольку ПДП может обеспечить время обмена одним байтом данных между памятью и ВЗУ, равное циклу обращения к памяти.

Для реализации режима прямого доступа к памяти необходимо обеспечить непосредственную связь контроллера ПДП и памяти ЭВМ. Для этой цели можно было бы использовать специально выделенные шины адреса и данных, связывающие контроллер ПДП с основной памятью. Но такое решение нельзя признать оптимальным, так как это приведет к значительному усложнению ЭВМ в целом, особенно при подключении нескольких ВЗУ. В целях сокращения количества линий в шинах ЭВМ контроллер ПДП подключается к памяти посредством шин адреса и данных системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП.

Способы совместного использования шин системного интерфейса процессором и контроллером ПДП

Можно выделить два основных способа ее решения: реализация обмена в режиме ПДП с "захватом цикла" и в режиме ПДП с блокировкой процессора.

Реализация обмена в режиме ПДП с "захватом цикла"

Существуют две разновидности прямого доступа к памяти с "захватом цикла". Наиболее простой способ организации ПДП состоит в том, что для обмена используются те машинные циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора. Однако возникает необходимость выделения таких циклов, чтобы не произошло временного перекрытия обмена ПДП с операциями обмена, инициируемыми процессором. В некоторых процессорах формируется специальный управляющий сигнал, указывающий циклы, в которых процессор не обращается к системному интерфейсу. При использовании других процессоров для выделения таких циклов необходимо применение в контроллерах ПДП специальных селектирующих схем, что усложняет их конструкцию. Применение рассмотренного способа организации ПДП не снижает производительности ЭВМ, но при этом обмен в режиме ПДП возможен только в случайные моменты времени одиночными байтами или словами.

Более распространенным является ПДП с "захватом цикла" и принудительным отключением процессора от шин системного интерфейса. Для реализации такого режима ПДП системный интерфейс ЭВМ дополняется двумя линиями для передачи управляющих сигналов "Требование прямого доступа к памяти" (ТПДП) и "Предоставление прямого доступа к памяти" (ППДП).

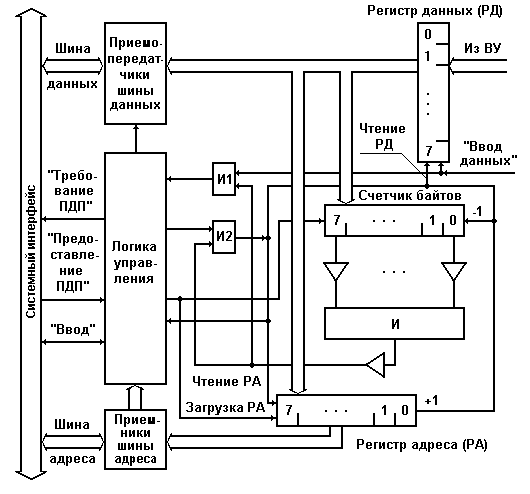

Принцип работы простого контроллера ПДП, обеспечивающего ввод данных в память ЭВМ по инициативе ВУ в режиме ПДП "Захват цикла"

Управляющий сигнал ТПДП формируется контроллером прямого доступа к памяти. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает на системный интерфейс управляющий сигнал ППДП и отключается от шин системного интерфейса. С этого момента все шины системного интерфейса управляются контроллером ПДП. Контроллер ПДП, используя шины системного интерфейса, осуществляет обмен одним байтом или словом данных с памятью ЭВМ и затем, сняв сигнал ТПДП, возвращает управление системным интерфейсом процессору. Как только контроллер ПДП будет готов к обмену следующим байтом, он вновь "захватывает" цикл процессора и т. д. В промежутках между сигналами ТПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы замедляется, но в меньшей степени, чем при обмене в режиме прерываний.

Применение в ЭВМ обмена данными с ВУ в режиме ПДП всегда требует предварительной подготовки, а именно: для каждого ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер, т. е. количество записываемых в память или читаемых из памяти байт (слов) информации. Следовательно, контроллер ПДП должен обязательно иметь в своем составе регистр адреса и счетчик байт (слов). Перед началом обмена с ВУ в режиме ПДП процессор должен выполнить программу загрузки. Эта программа обеспечивает запись в указанные регистры контроллера ПДП начального адреса выделенной ВУ памяти и ее размера в байтах или словах в зависимости от того, какими порциями информации ведется обмен. Сказанное не относится к начальной загрузке программ в память в режиме ПДП. В этом случае содержимое регистра адреса и счетчика байт слов устанавливается переключателями или перемычками непосредственно на плате контроллера.

Блок-схема простого контроллера ПДП, обеспечивающего ввод данных в память ЭВМ по инициативе ВУ в режиме ПДП "Захват цикла", приведена на рис. 1.

Рис. 1. Контроллер ПДП для ввода данных из ВУ в режиме "Захват цикла" и отключением процессора от шин системного интерфейса

Перед началом очередного сеанса ввода данных из ВУ процессор загружает в регистры его контроллера следующую информацию: в счетчик байт - количество принимаемых байт данных, а в регистр адреса - начальный адрес области памяти для вводимых данных. Тем самым контроллер подготавливается к выполнению операции ввода данных из ВУ в память ЭВМ в режиме ПДП.

|

Из за большого объема этот материал размещен на нескольких страницах:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 |